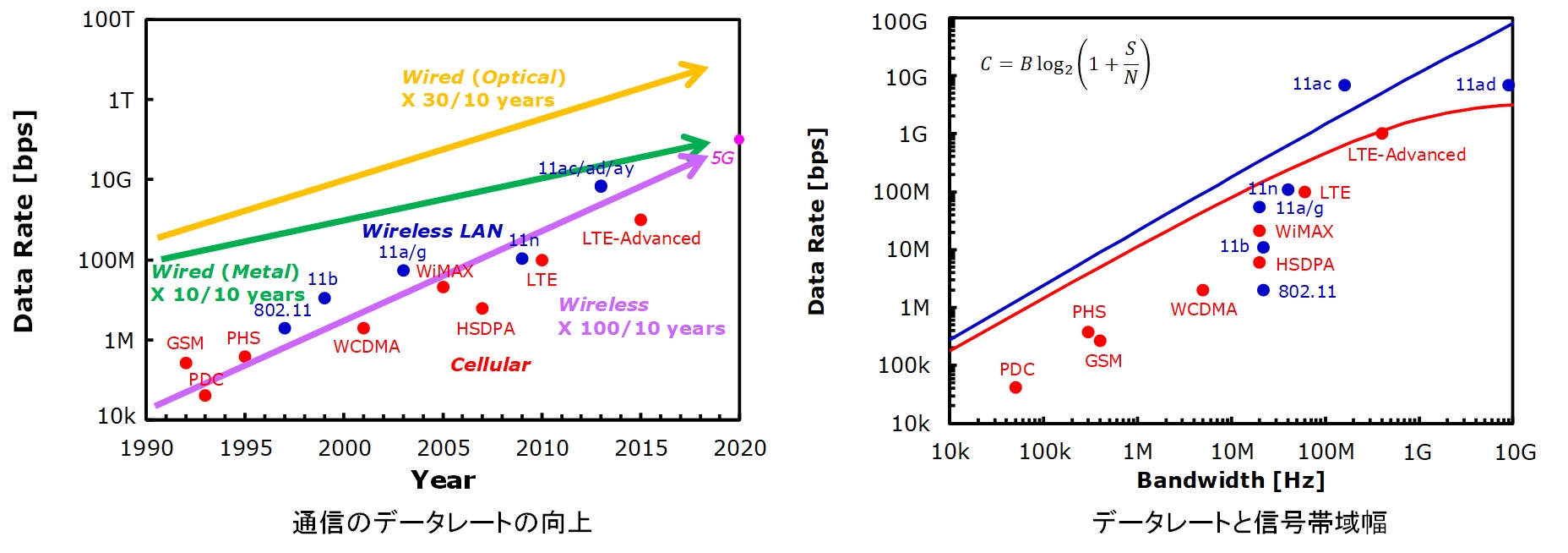

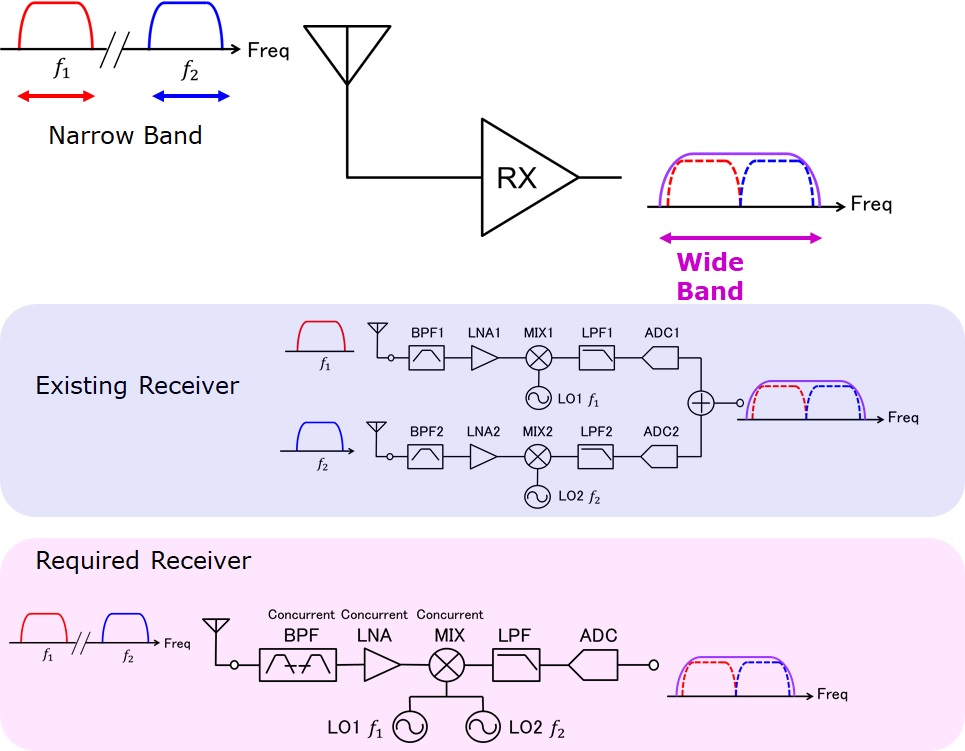

(i)で課題となるのは、トランシーバ回路が増大することにより、消費電力・チップサイズ(コスト)が増大すること、(ii)で課題となるのは雑音特性が悪くなる、微細プロセスが必要となりコストが増大することである。ここでは、以下について紹介する。

1. Carrier Aggregation対応受信器

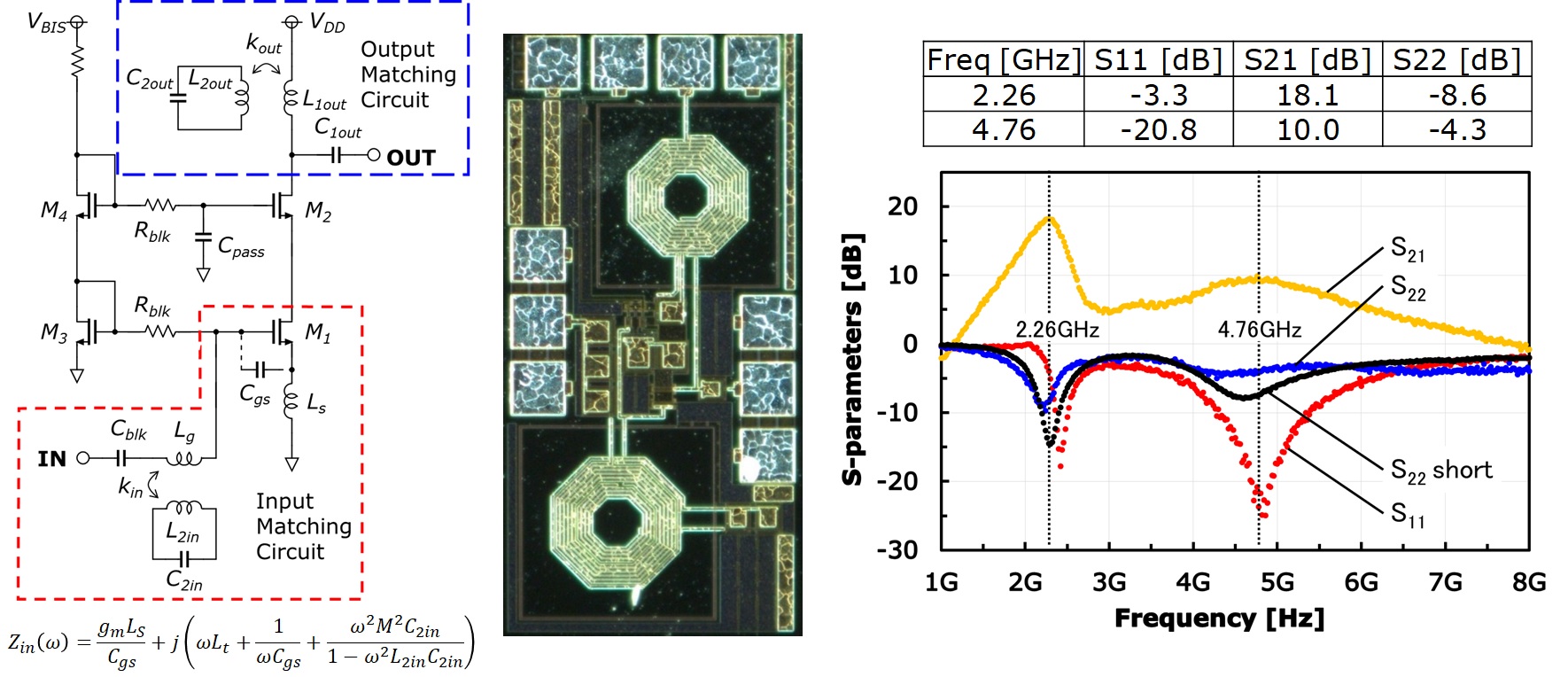

1-1. CA対応受信LNAの実現例1(電流再利用型)

1-2. CA対応受信LNAの実現例2(相互誘導整合回路型)

2. 20〜40GHz発振器の低位相雑音化

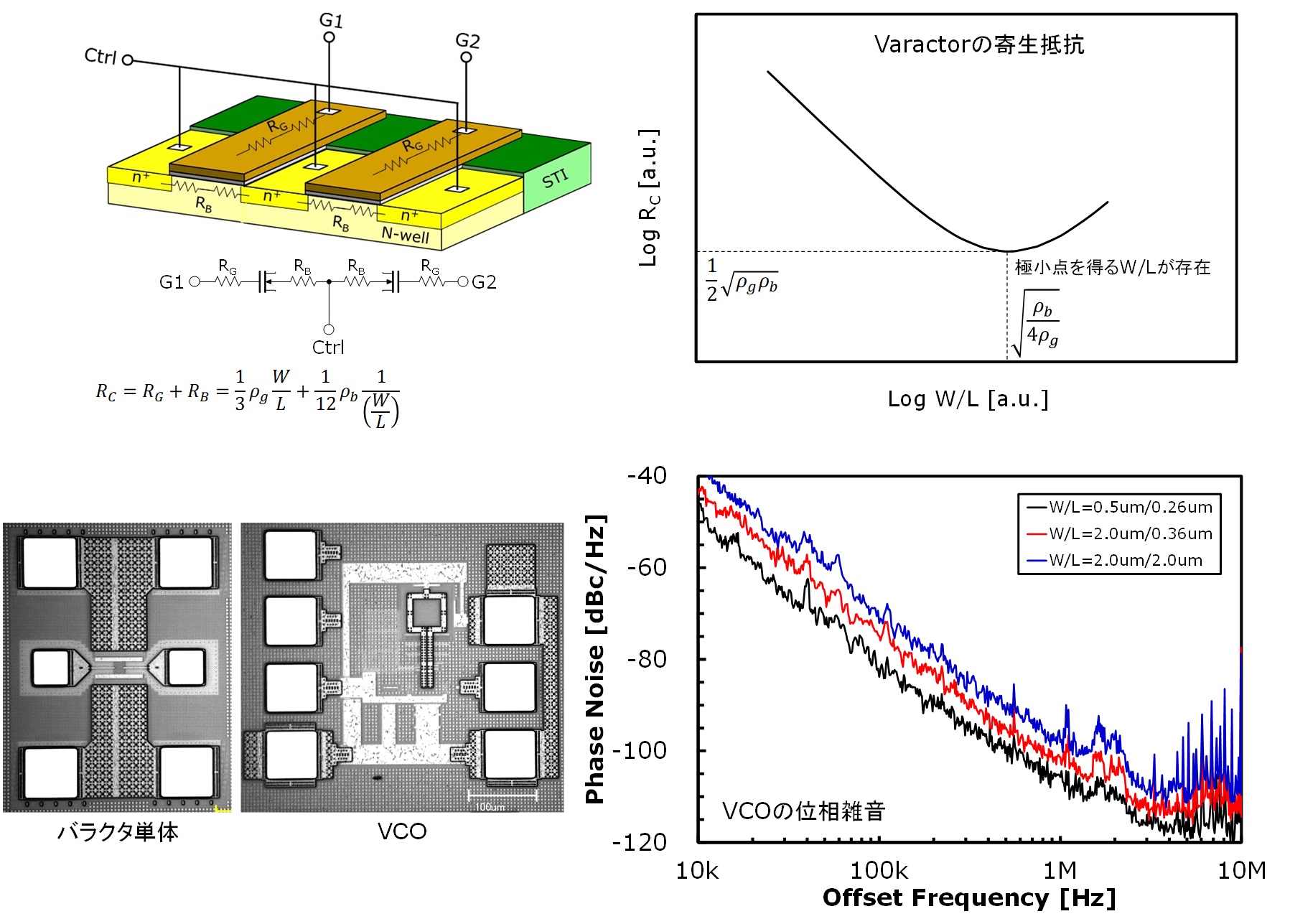

2-1. バラクタのQ値改善

2-2. インダクタの低寄生抵抗化

2-3. 2D-Striped Inductorによる低寄生抵抗化

2-4. 2D-Striped InductorによるVCOの低位相雑音化

2-5. 3D-Striped InductorによるVCOの低位相雑音化

2-6. 3D-Striped Inductorの最適化

3. ローコストプロセスを用いた高周波増幅器

3-1. ゲート・ドレイン間にインダクタを挿入した回路

1. Carrier Aggregation対応受信器

トランシーバ回路の増大を防ぐために、ひとつの回路で複数のキャリアをconcurrentに受信できる回路が必要であるため、以下の様な二波同時受信LNAの研究を進めている。

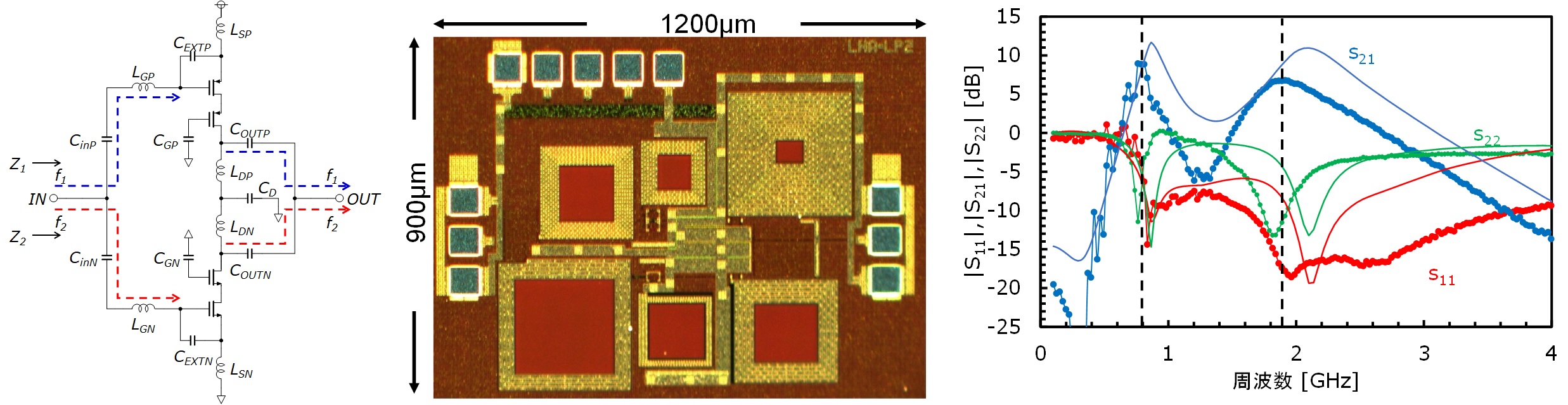

NMOSカスコード増幅器(2.1GHz)とPMOSカスコード増幅器(860MHz)を接続し電流再利用型とした増幅器

2. 20〜40GHz発振器の低位相雑音化

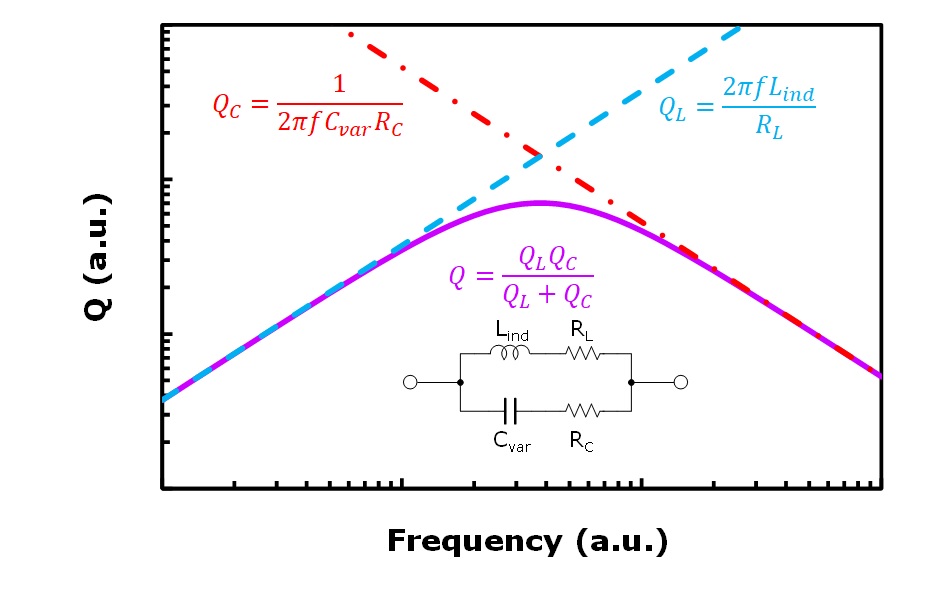

LC発振器の低雑音化において最も重要なパラメータはLC共振器のQ値を高くする(寄生抵抗を減少させる)ことである。が、下図のようにインダクタのQ値は高周波数化とともに上昇するが、キャパシタのQ値は高周波数化とともに劣化するため、共振器のQ値は、ある周波数で極大値を取る。この極大値をとる周波数を高周波化するため、キャパシタ(バラクタ)のQ値の改善、インダクタのQ値の改善を検討している。

バラクタの寄生抵抗はゲート側(ゲート抵抗)とバックゲート側(基板抵抗)のLW依存性が互いに異なるため、W/Lにより極小値(最適値)を得る。それを実験的に確かめ、その結果からW/L=0.5um/0.26um(本研究での最適値)、2.0um/0.36um、2.0um/2.0umの3種類のバラクタをもつVCOを設計・試作し、位相雑音を測定したところ右下図のように低位相雑音化が達成された。

Y. Itano, S. Morimoto, S. Yoshitomi, and N. Itoh, "High-Q MOS Varactor Models for Quasi-Millimeter-Wave Low-Noise LC-VCOs," IEICE Transaction on Fundamentals, vol. E97-A, No.3, pp. 759-767, Mar. 2014

このページのトップへ

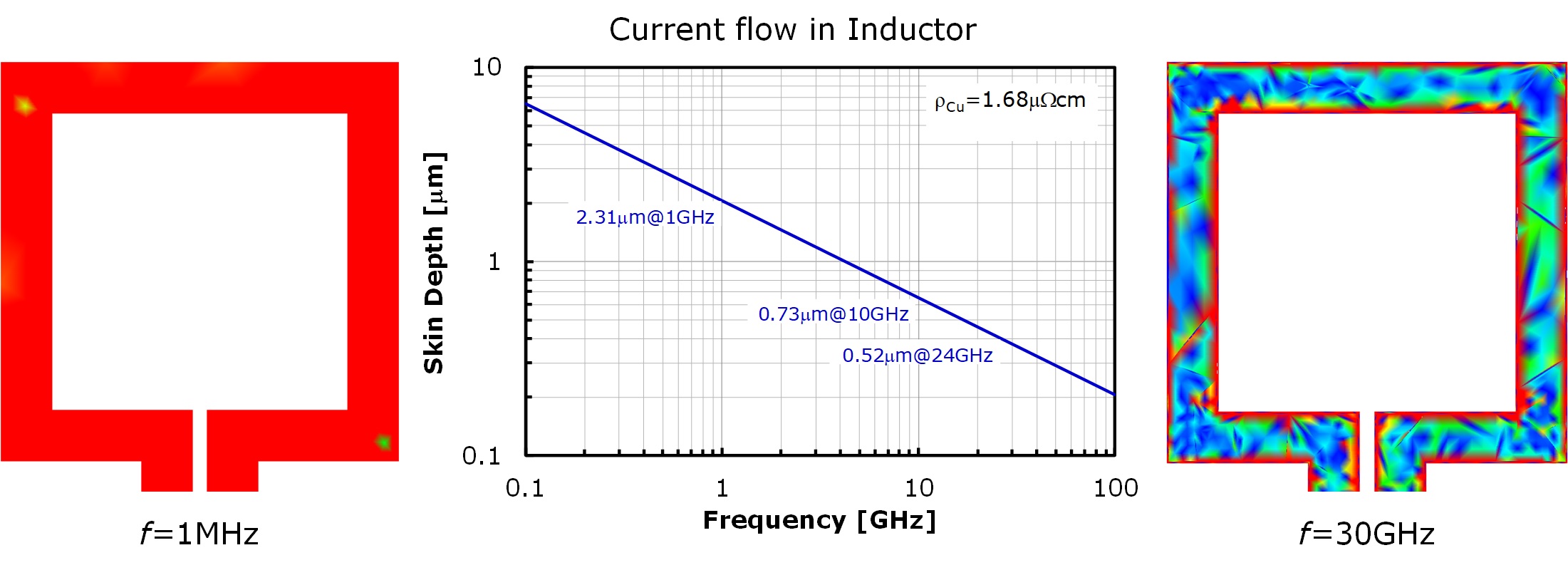

高周波領域では電流は金属配線全体を流れずにその周辺部分に偏在する(表皮効果)。したがって、寄生抵抗が非常に高くなる。

そこで我々は2Dおよび3D的にメタル分割を行い、周辺長を長くしたStriped Inductorの研究を行っている。

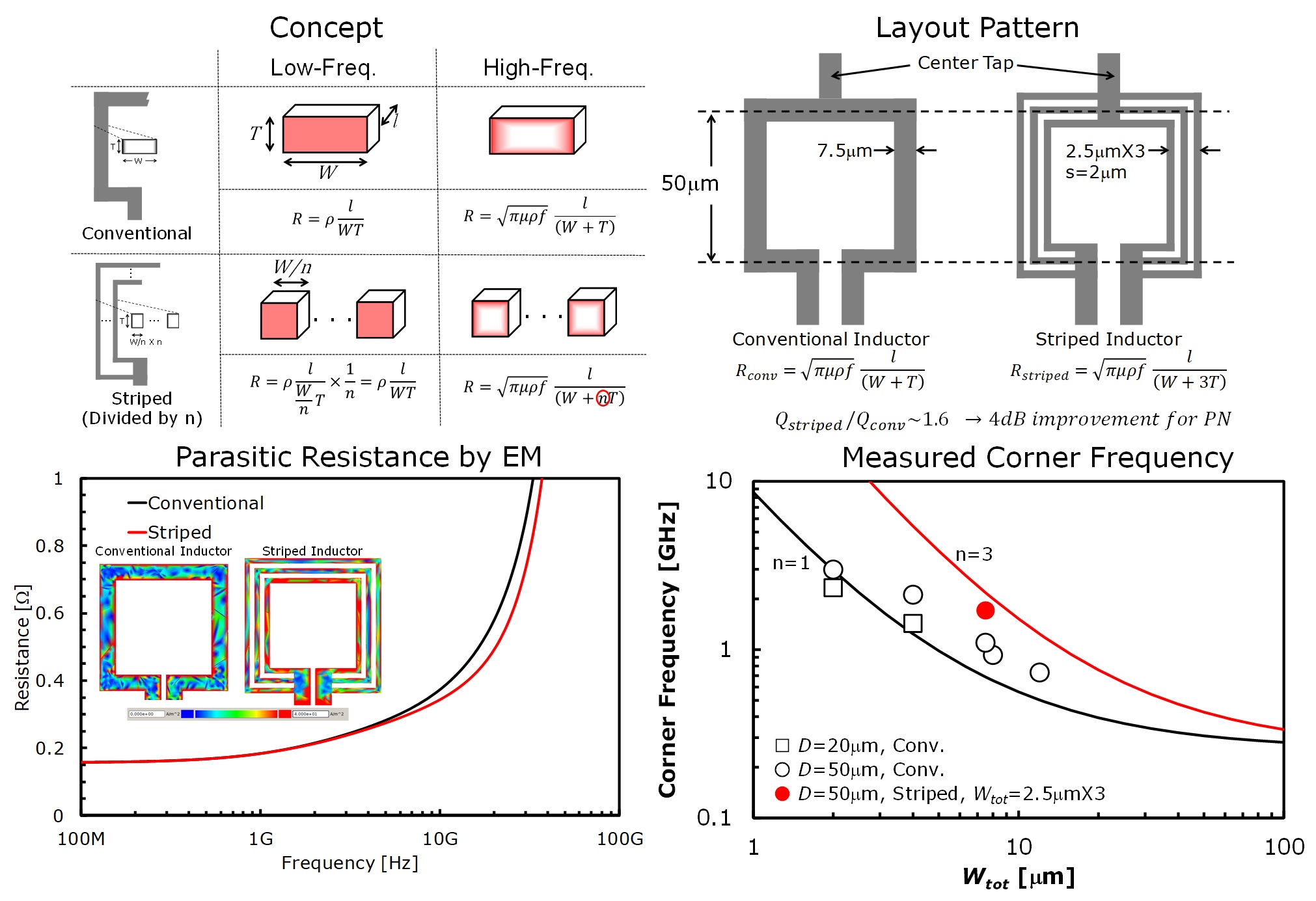

2D-Striped Inductorのコンセプトは、インダクタ配線の周辺長を長くすることにより寄生抵抗を低下させることである。左上図のように、通常構造の寄生抵抗とStriped構造の寄生抵抗は計算され、右上図のレイアウトとすると約4 dB位相雑音の低下が期待できる。電磁界シミュレーションを用いて寄生抵抗の差をプロットしたのが左下図であり、7〜8GHzからStriped構造の優位性が確認でき、インダクタ単体の測定値から求めたコーナー周波数(表皮効果が顕在化する周波数)は通常構造と比較して、高周波化していることが判る。

H. Tsuji, Y. Itano, K. Komoku, T. Morishita, S. Yoshitomi, and N. Itoh, "Millimeter-Wave VCO using Striped Inductor," Proc. of Asia-Pacific Microwave Conference (APMC2014) 2014, pp. 959-961, Sendai, Nov. 2014.

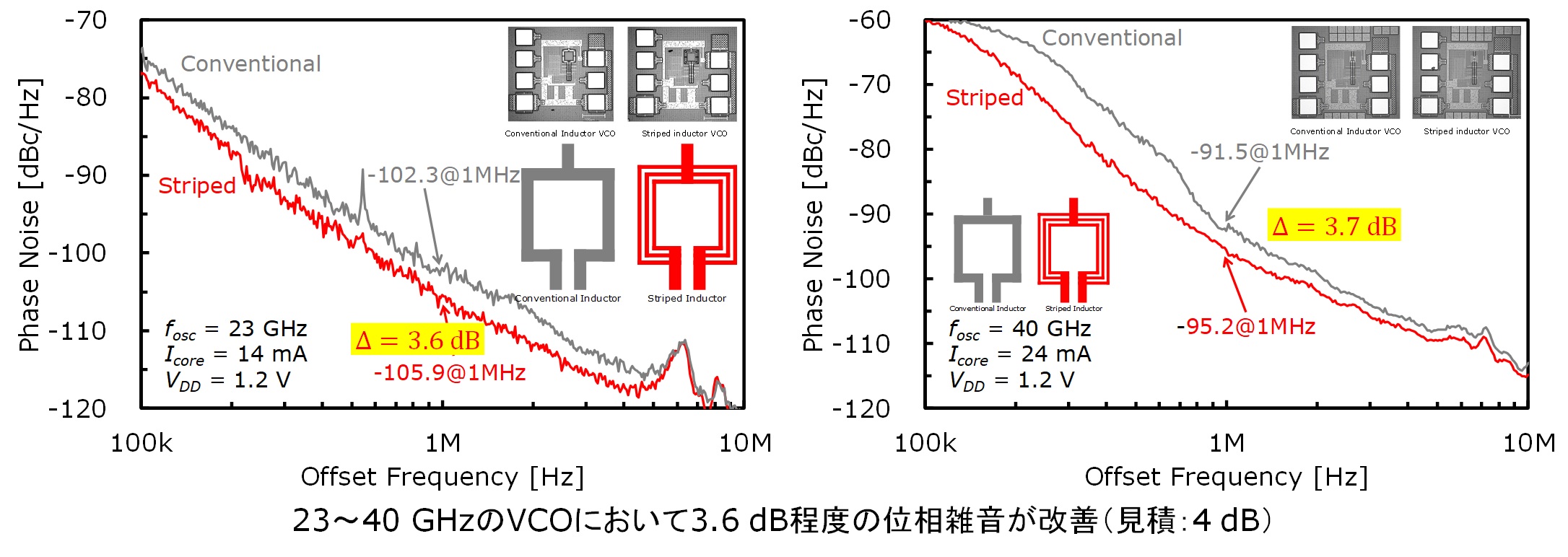

2D-Striped Inductorを用いて23GHzと40GHzのVCOを設計・試作した。同時に設計・試作した通常構造のインダクタを用いたVCOの位相雑音と比較して3.6dB前後の位相雑音の改善が認められ、本構造の優位性を確認することができた。

N. Itoh, H. Tsuji, Y. Itano, T. Morishita, K. Komoku, and S. Yoshitomi, “A Study of Striped Inductor for K- and Ka-band Voltage-controlled Oscillators,” IEICE Transaction on Electronics, Vol.E99-C, No.6, pp.614-622, Jun. 2016, DOI: 10.1587/transele.E99.C.614.

このページのトップへ

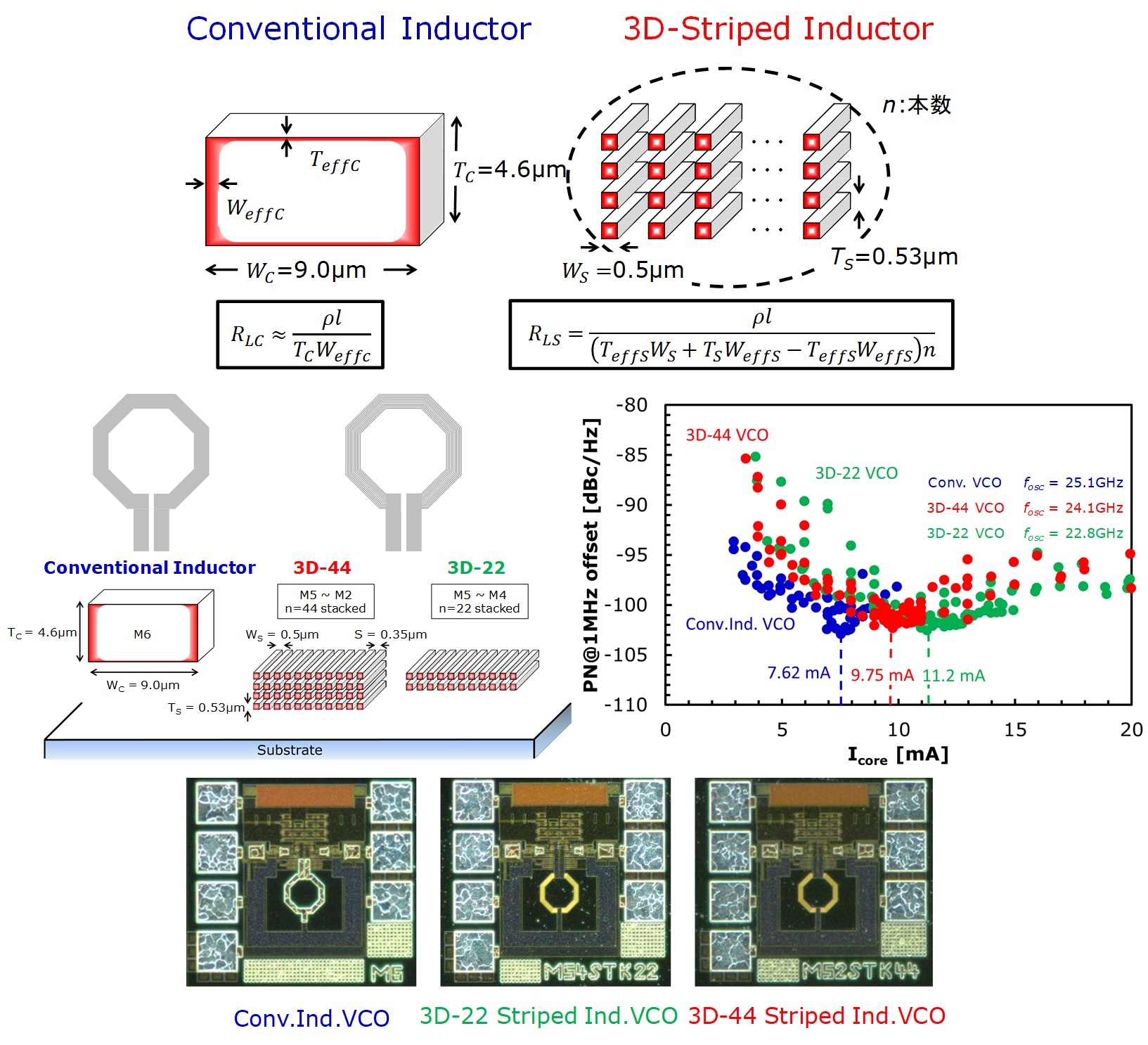

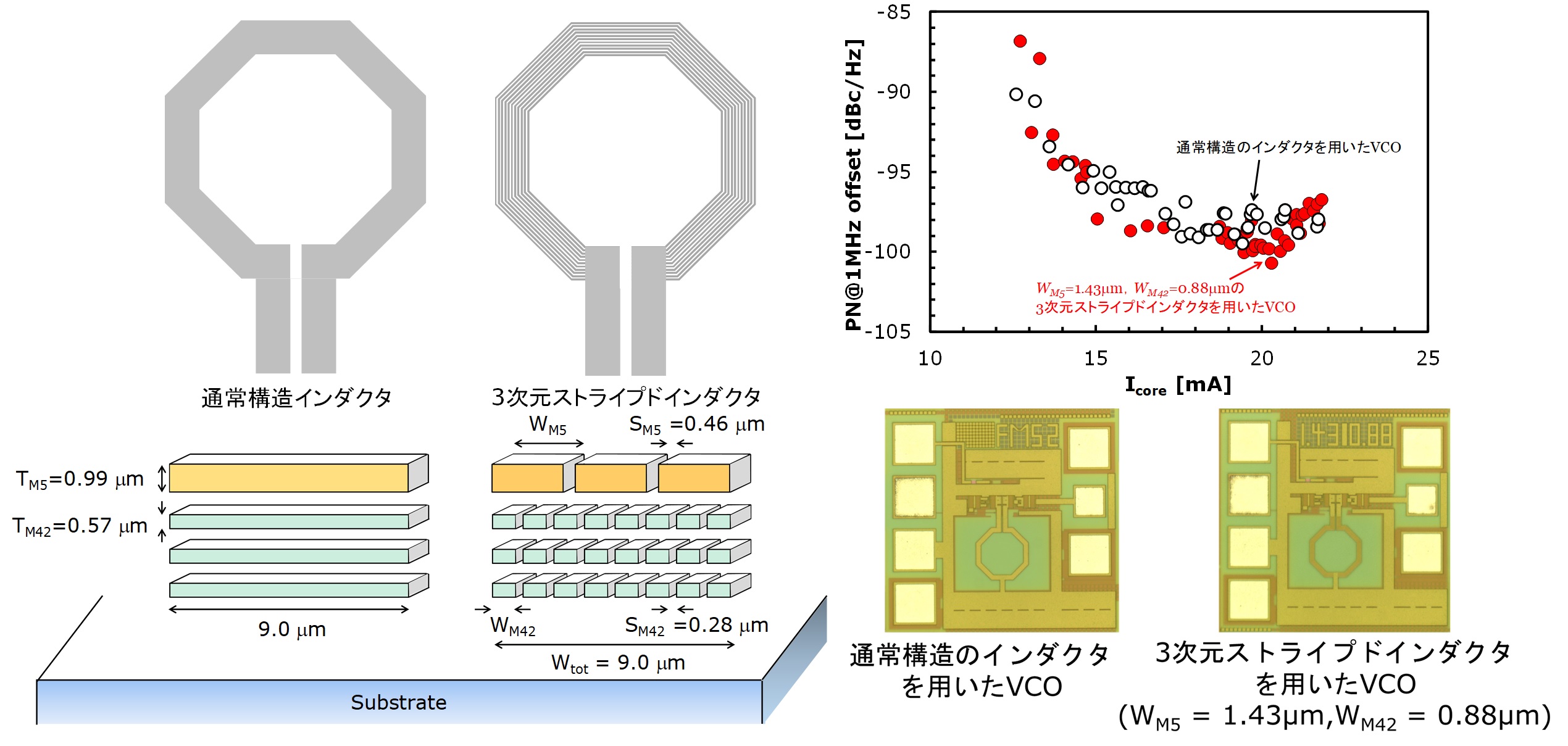

2D-Striped Inductorのコンセプトをさらに拡張して3D-Striped Inductorを検討した。ここでは、厚膜メタル1層を用いた通常構造のインダクタと、薄膜メタル4層を用いた3D-Striped Inductorとの比較をおこなった。結果は下記の様に、薄膜メタル4層を用いた3D-Striped Inductorを用いたVCOは通常構造のインダクタを用いたVCOに対して、ほぼ同じ位相雑音を約20%程度の電流増加で達成することができた。

Y. Sakamoto, K. Komoku, T. Morishita, N. Itoh, “24 GHz Low-Phase-Noise VCO Using 3D-Striped Inductor Utilized Thin-Metal Layers,” Proc. of the 2017 Asia-Pacific Microwave Conference, TH3-E, Kuala Lumpur, Nov. 2017.

このページのトップへ

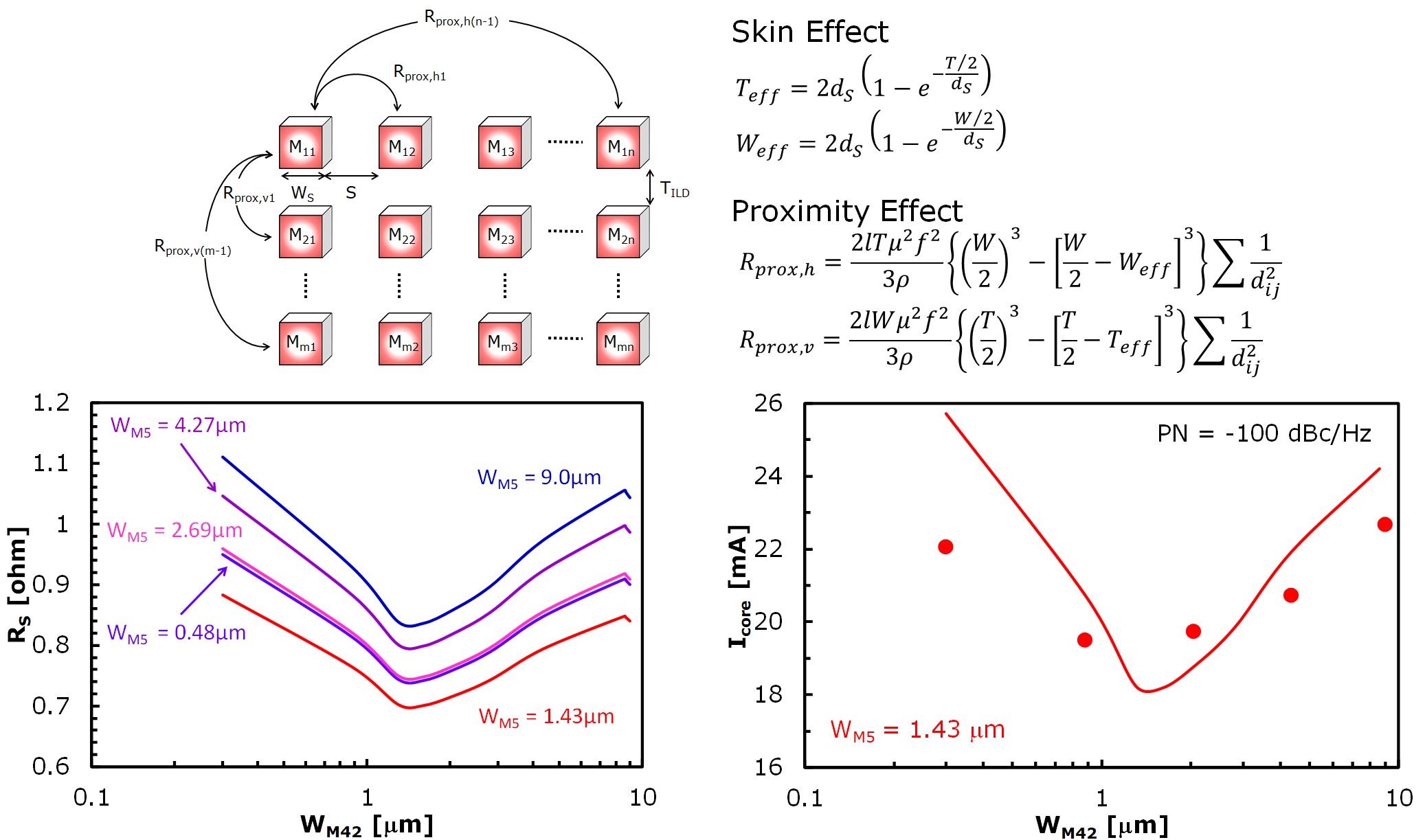

3D-Striped Inductorでは、近接するメタルストライプが多いため、表皮効果とともに近接効果についても考慮する必要がある。ここで、全体のメタル幅が9umで一定のもと、M5のストライプ幅を一定としてM4〜M2のストライプ幅を横軸に、寄生抵抗を縦軸にプロットする(左下図)と、寄生抵抗値はある幅で極小値をとることが判る。また、設計・試作したVCOの1MHz離調における位相雑音が−100dBc/Hzに達する電流も同じ傾向となる(右下図)。これらの結果から、横軸の左側(ストライプ幅が狭い)では相対的にスペースの下図が多いので近接効果が支配的となり、右側では表皮効果が支配的になることがわかる。

坂本 裕太,小椋 清孝,森下 賢幸,伊藤 信之,”3次元ストライプドインダクタの最適化による低位相雑音電圧制御発振器の検討,” 電子情報通信学会論文誌C,Vol.J103-C,No.1,pp.xxx-xxx,Jan. 2020.(採録決定)

このページのトップへ

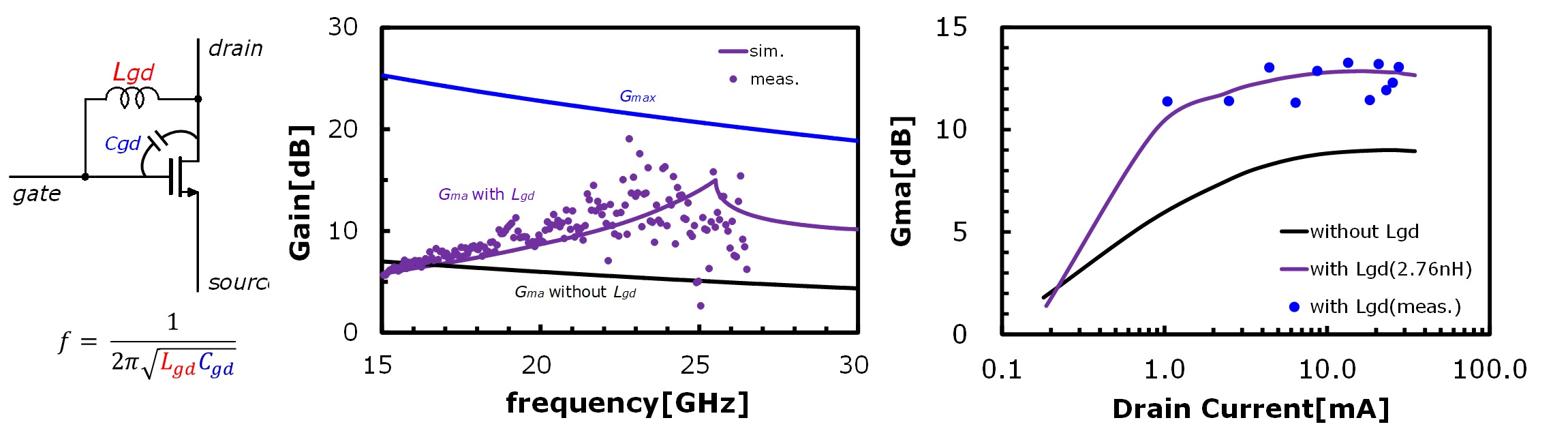

3. ローコストプロセスを用いた高周波増幅器

高周波増幅器を実現するには、通常fTの高いトランジスタを用いる必要があり、一般には動作周波数の10倍のfTが必要と言われている。しかしながら、例えば24GHzの増幅器を実現しようとすると、fT=240GHzが必要となり、これはCMOSのプロセスで言うと40nmプロセス程度となりコストがかかる。そこで、180nm程度のプロセスで24GHzの増幅器が実現できないかの検討を行っている。

Y. Sato, K. Komoku, T. Morishita, N. Itoh, “A 24-GHz Low-Noise Amplifier using Three-Port Inductor,” The 19th International Conference on Analog VLSI Circuits (AVIC2016), pp.103-106, Boston, Aug. 2016.